White Paper

Authors:

Sascha Lohse (Finetech GmbH & Co. KG)

Alexander Wollanke (Fraunhofer IZM-ASSID)

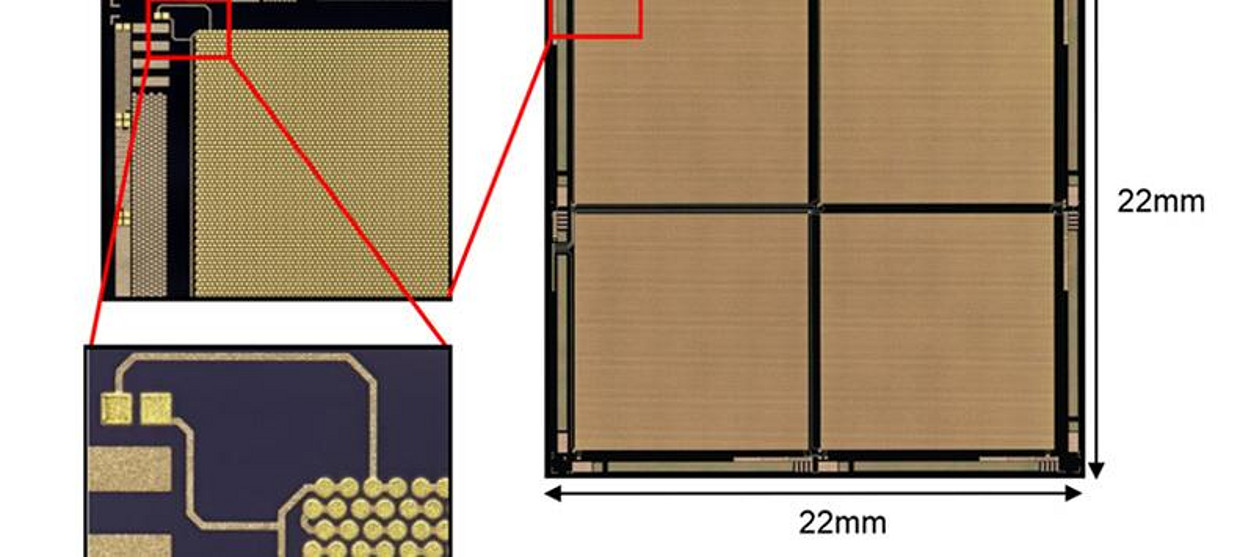

Abstract: Tougher requirements related to the request for smaller, lighter and multi-functional electronic devices impose increased demands on IC packaging. Ever more complex circuitry, fine pitch and micro bump designs and die stacking are examples of how the industry meets these demands. Finding a suitable process technology for 3D packaging can be a challenge. This paper provides information about various connection methods predominantly used in today’s 3D packaging. In comprehensive trials, various dies characterized by high bump count (up to 143,000), fine pitch (down to 25 μm) and small bump diameter (down to 13 μm) were placed on a substrate using a FINEPLACER® sigma bonder. This whitepaper describes test procedures for different 3D integration technologies and presents utilized process parameters and results.