White Paper

Authors:

Lyubomir Kerachev, Yves Lembeye, Jean-Christophe Crébier (Grenoble Electrical Engineering Laboratory)

Christoph Daedlow (Finetech GmBH & Co. KG)

Abstract

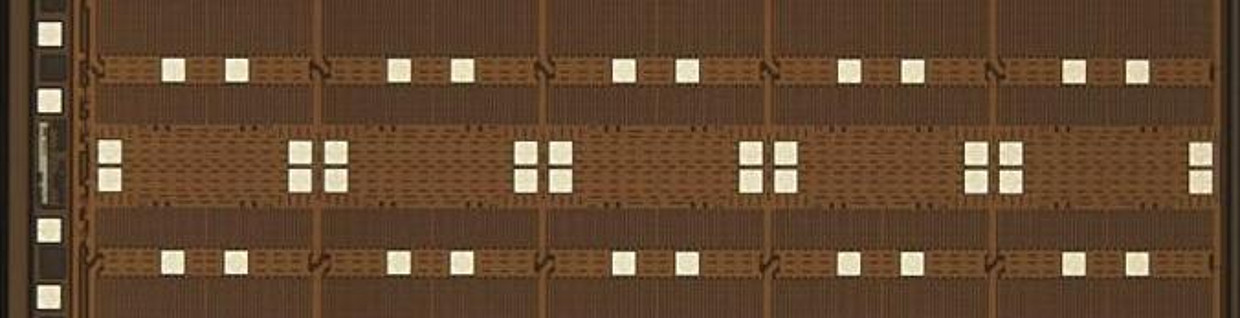

Standard IC packages with an increased number of I/O pads suffer from larger volume, increased cost, increased wire bonding resistances and parasitic inductances while offering normalized assembly requirements. Flip-chip bonding allow significant downsizing of chip package, reducing the assembly cost and decreasing the parasitic phenomena such as pad resistances and inductances. In addition, it reduces the number of thermal interfaces between the chip and the substrate which operates as the principal heat removal path. This paper deals with the tests for the characterization of commercially available technologies for micro assemblies such as anisotropic adhesive bonding, thermocompression bonding, thermosonic/ultrasonic bonding and solder bonding. Custom flip-chip bonding technique inspired by the solder bumping technology is also proposed and experimentally characterized. The aim of this work is to determine the most suitable flip-chip bonding technology for CMOS circuits with increased number of pads and complex land patterning.